## **Features**

- Versatile Serial Bus Interface

- Four separate I2C busses

- SPI

- Dallas 1 Wire

- SCL Stretch to work with software & microprocessor slaves

- Interrupt input

- adjustable I2C speed

- ASCII protocol for ease of use

- Automatic I2C Deadlock Recovery

- Spare I/O pins for user control functions

- Hi Speed RS232: 1200bd 921k

- Fully buffered RS232

- Compact 18 pin package

- Low power

- Low EMC

- Sleep

- Watchdog function detects and actions host computer failure

- 3-5V

- Cross-Platform

## **Applications**

- Evaluation Boards for I2C chips

- Rapid Prototyping & PnP design

- PC based instrumentation and control

- ATE for I2C based equipment

- Isolated I/O

- Cheap and Easy Data logging

- PC and Network Watchdogs

- Handheld computer / calculator Analog/Digital I/O

- RF Systems with EMI constraints

- Education

- RS232 Parallel port chip

- Evaluation of I2C and SPI chips

## **Programmable**

EEProm stores commands and settings

- Power On Reset actions

- Interrupt actions

- Watchdog timeout actions

- Macro's

- Autonomous actions

- Baud Rate (1200bd-921k)

- Settings

## 1 Description

BL233 is a simple and effective way to use I2C devices from any computer and OS. Fully built RS232/USB adaptors are available. No DLL's or special libraries are needed to use it.

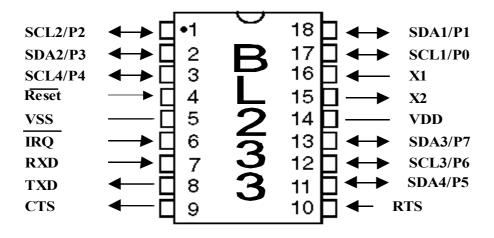

Figure 1: BL232/3 Pinout (DIP 18, SO-18)

## **Table of Contents**

| <u>FEATURES</u>                                                | 1         |

|----------------------------------------------------------------|-----------|

| APPLICATIONS                                                   | 1         |

|                                                                |           |

| PROGRAMMABLE                                                   | 1         |

| 1 DESCRIPTION                                                  | 1         |

| 2 TABLE 1: BL233 PINOUT DESCRIPTION                            | 5         |

| 2 TABLE 1, BL255 TINOUT DESCRIPTION                            |           |

| <u>3 12C BUSSES</u>                                            | 5         |

| 3.1 Threshold Levels and Supply Voltage                        | 6         |

| 3.2 Bit Timing.                                                |           |

| 3.3 SCL Stretch.                                               |           |

| 3.4 Four Wire Bus.                                             | 6         |

| 3.5 Fast Mode.                                                 |           |

| 3.6 Multimaster Arbitration.                                   | 7         |

| 4 TABLE 2: COMMAND CHARACTER LIST                              | 8         |

|                                                                |           |

| 5 COMMAND FORMAT                                               | 9         |

| 5.1 A SIMPLE I2C Transaction.                                  | g         |

| 5.2 Stop.                                                      |           |

| 5.3 Reading I2C                                                |           |

| 5.3.1 Reading an indeterminate number of bytes: Pascal Strings |           |

| 5.4 10 Bit Addresses.                                          |           |

| 5.5 R and W: Fast Read/Write Commands.                         |           |

| 5.6 Selecting the I2C Bus.                                     | 10        |

| 5.7 Delaying.                                                  |           |

| 5.8 Pause Command for Timing Critical Sequences.               |           |

| 5.9 I2C Acknowledge.                                           |           |

| <u>5.9.1 Writing</u>                                           |           |

| <u>5.9.2 Reading</u>                                           | 12        |

| 6 STATUS AND CONTROL REGISTERS                                 | 13        |

| 6.1 Setting Control Register and Bus Timing                    |           |

| 6.1.1 Bus Timing Value.                                        |           |

| 6.2 Querying Status Register.                                  |           |

| 6.3 Interrupt Pin.                                             |           |

| 6.4 Return a Char.                                             |           |

| 7 MESSAGE NUMBERS                                              | 15        |

|                                                                |           |

| 8 DIRECT PIN I/O                                               | 16        |

| 8.1 Reading Pins                                               | 16        |

| 8.2 Writing Pins.                                              |           |

| 8.2.1 Pin Timing                                               | 16        |

| 9 SPI                                                          | 17        |

| <u>7 01 1</u>                                                  | , <b></b> |

# **BL233B**

## RS232 – I2C/SPI/1Wire Adaptor & Controller

| 9.1 CS/Strobe Pins.                                                         |    |

|-----------------------------------------------------------------------------|----|

| 9.1.1 CS Pins and commands for I2C-2-PC.                                    |    |

| 9.2 THE DATA PINS SDA VS MOSI / MISO                                        |    |

| 9.3 Short Data.                                                             |    |

| 9.4 Bidirectional (simultaeneous) Write/Read.                               |    |

| 9.5 SPI Clock Polarity                                                      |    |

|                                                                             |    |

| 10 1WIRE BUS                                                                | 19 |

| <u>10.1 Pins</u> .                                                          | 20 |

| 10.2 Software.                                                              | 20 |

| 11 EEPROM MEMORY                                                            | 20 |

| 11.1 Table 4: EEProm Memory Map                                             | 20 |

| 11.2 Macros.                                                                |    |

| 11.3 A Macro for combined 8 switches + 8 Leds board.                        |    |

| 11.4 A SIMPLE "PROGRAM"                                                     |    |

| 11.5 Writing the EEProm.                                                    |    |

| 11.5.1 Write Protecting the EEProm.                                         |    |

| 11.6 Dumping the EEProm.                                                    | 22 |

| 12 SERIAL COMMS                                                             | 22 |

| 12.1 Data Format.                                                           |    |

| 12.1.1 HiCharsAsAscii.                                                      |    |

| 12.7.7 Michaelsasascu.<br>12.2 Handshaking.                                 |    |

| 12.3 Table 5: Serial Initalisation Registers in EEProm.                     |    |

| 12.4 Baud Rate.                                                             |    |

| 12.4.1 Special Pins Mode and Baud Rate Changing Problems.                   |    |

| 12.5 Max Baud Rate and Speed.                                               |    |

| 12.5.1 PC Serial Port Latency.                                              | 24 |

| <u>12.5.2 RS232 Drivers</u>                                                 |    |

| 12.6 Serial Buffer Size.                                                    |    |

| <u>12.7 USB.</u>                                                            |    |

| 12.8 EOL, Separator Chars, and Data Formatting                              |    |

| 13 OSCILLATOR                                                               | 25 |

| 13.1 Timer.                                                                 | 25 |

| 13.2 1-Wire Timing.                                                         | 25 |

| 14 WATCHDOG.                                                                | 26 |

|                                                                             |    |

| 14.1 Uses                                                                   |    |

| <u>15 RESET</u>                                                             | 26 |

| 15.1 Low Voltage Reset.                                                     | 26 |

| 15.2 Power On Reset Macro.                                                  | 26 |

| 16 SLEEP MODE                                                               | 26 |

|                                                                             |    |

| 16.1 Pause and Sleep.                                                       |    |

| 17 I2C BUS CONNECTORS AND PINOUTS                                           | 27 |

| 18 I2C BUS DEADLOCK                                                         | 27 |

|                                                                             |    |

| 18.1 Added/Dropped Clock Pulses. 18.2 Failure to send NACK after last read. |    |

| 18.3 BL233B Automatic STOP Recovery                                         |    |

| 18.4 Demonstrating the Problem.                                             |    |

| 10. DEMONSTRATING THE TROBLEM.                                              | 20 |

# **BL233B**

## RS232 – I2C/SPI/1Wire Adaptor & Controller

| 18.4.1 Extra Clock Pulse                                       | 28 |

|----------------------------------------------------------------|----|

| 18.4.2 Failure to send NACK.                                   |    |

| 18.5 Manually Checking SDA and SCL                             |    |

| 19 GETTING STARTED                                             | 29 |

|                                                                |    |

| 20 EXAMPLE APPLICATIONS                                        | 30 |

| 20.1 I2C-2-PC: Dual Interface USB & RS232 to I2C Adaptor       |    |

| 20.2 SIMPLE I2C TO RS232 ADAPTOR.                              |    |

| 20.3 I2C EEProms; Dumping                                      |    |

| <u>20.3.1 24C01</u>                                            |    |

| <u>20.3.2 24C02</u>                                            |    |

| <u>20.3.3 24C04</u>                                            |    |

| <u>20.3.4 24C16</u>                                            |    |

| <u>20.3.5 24C64</u>                                            |    |

| 20.4 SIMPLE DATA LOGGER WITH NO PC SOFTWARE                    |    |

| 20.5 ISOLATING AN I2C Bus.                                     |    |

| 20.6 RS232 TO LCD MODULE ADAPTOR                               |    |

| 20.7 Huge RS232 Parallel Port.                                 |    |

| 20.8 HARDWARE WATCHDOG FOR NETWORK OR SERVER                   |    |

| 20.8.1 Circuit                                                 |    |

| 20.8.2 Operation.                                              |    |

| 20.8.3 Code                                                    |    |

|                                                                |    |

| 21 MIGRATION TO BL233_B.                                       | 34 |

| 21.1 BL233 А то BL233 В.                                       | 34 |

| 21.1.1 Wait for EOL ":"                                        | 34 |

| 21.1.2 I2C Stop Deadlock Automatic Recovery.                   |    |

| 21.1.3 1-Wire Buses Fixed.                                     | 34 |

| 21.1.4 RTS Input Fixed.                                        |    |

| 21.1.5 XON/XOFF Added.                                         | 34 |

| 21.1.6 Reset Macro not executed in Special Pins Mode           |    |

| 21.1.7 Stop always follows reads correctly                     |    |

| 21.1.8 Improved Formatting of Data                             |    |

| 21.1.9 Hi Chars can be used                                    |    |

| 21.1.10 N Command documented                                   |    |

| 21.1.11 Internal Reset                                         |    |

| <u>21.1.12 BL232 B</u>                                         | 35 |

| <u>22 ERRATAE</u>                                              | 35 |

| 22.1 BL233 B                                                   | 35 |

| 22.2 BL233 A.                                                  |    |

| 23 ORDERING INFORMATION                                        | 35 |

|                                                                |    |

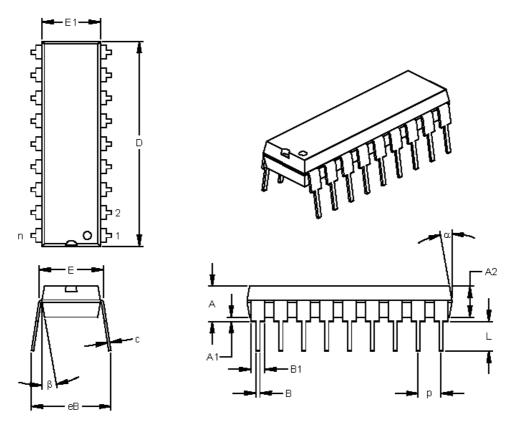

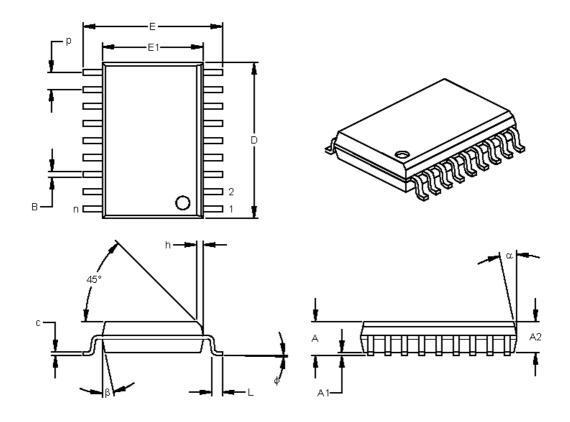

| 24 PACKAGE DIMENSIONS                                          |    |

| 24.1 18-Lead Plastic Dual In-line (P) — 300 mil (PDIP)         |    |

| 24.2 18-Lead Plastic Small Outline (SO) — Wide, 300 mil (SOIC) |    |

| 24.3 SSOP ETC.                                                 | 37 |

| 25 CO-OPERATION                                                | 38 |

## 2 Table 1: BL233 Pinout Description

| Name    | DIP<br>Pin | SSO<br>P Pin | I/O/P<br>Type     | Buffe  | User<br>Pin | Description                       |    |

|---------|------------|--------------|-------------------|--------|-------------|-----------------------------------|----|

|         | #          | #            | Type              | Type   | F 111       |                                   |    |

| SCL1    | 17         | 19           | I/oc <sup>1</sup> | $ST^2$ | I/0         | I2C Bus #1                        | P0 |

| SDA1    | 18         | 20           | I/oc              | ST     | I/0         | I2C Bus #1, 1 Wire                | P1 |

| SCL2    | 1          | 1            | I/oc              | ST     | I/0         | I2C Bus #2                        | P2 |

| SDA2    | 2          | 2            | I/oc              | ST     | I/0         | I2C Bus #2                        | P3 |

| SCL4    | 3          | 3            | In                | ST     | I/oc        | I2C#4, SPI#2 CS pin, 1Wire        | P4 |

| _Reset_ | 4          | 4            | In                | ST     | In          |                                   |    |

| Vss     | 5          | 5,6          |                   |        |             |                                   |    |

| Int     | 6          | 7            | In                | TTL    | I/0         | 0=interrupt                       |    |

| RXD     | 7          | 8            | In                | ST     |             | RS232 data IN, Connect to PC      |    |

|         |            |              |                   |        |             | TXD                               |    |

| TXD     | 8          | 9            | Out               |        |             | RS232 data Out, Connect to PC     |    |

|         |            |              |                   |        |             | RXD                               |    |

| CTS     | 9          | 10           | Out               |        | I/0         | Connect to PC CTS, Tells PC to    |    |

|         |            |              |                   |        |             | send                              |    |

| RTS     | 10         | 11           | IN                | TTL    | I/0         | Connect to PC RTS, PC controls    |    |

|         |            |              |                   |        |             | me.                               |    |

|         |            |              |                   |        |             |                                   |    |

| SDA4    | 11         | 12           | I/O               | TTL    | I/0         | I2C#4, SPI#3 CS pin, 1Wire        | P5 |

| SCL3    | 12         | 13           |                   | TTL    | I/0         | I2C Bus #3                        | P6 |

| SDA3    | 13         | 14           |                   | TTL    | I/0         | I2C Bus #3, 1 Wire                | P7 |

| VDD     | 14         | 15,1         |                   |        |             |                                   |    |

|         |            | 6            |                   |        |             |                                   |    |

| X2 Out  | 15         | 17           |                   |        |             | Crystal / Oscillator Out          |    |

| X1 In   | 16         | 18           | 11 1              |        |             | Crystal / Oscillator In (14.7456) |    |

Unused pins should be pulled up.

See also 12.4.1 Special Pins mode.

## 3 I2C Busses

The BL233 supports up to 4 physical 2 wire I2C Busses. (1-4)

Two operate with Schmitt-CMOS levels, and 2 with TTL levels.

Only one bus can be active at one time. The bus will be put into Stop (P) state before selecting the new bus.

Bus numbers above 4 are logical busses, ie they map to the same pins as another bus, or work differently

- Full Split Bus, Separate in and out pins for both SDA and SCL

- Half split, Separate SDA IN pin

- FAST (400kHz) timing busses

<sup>&</sup>lt;sup>1</sup> Open Collector drive when used for I2C bus

<sup>&</sup>lt;sup>2</sup> Schmitt Trigger

#### • 1-Wire busses

SPI works on I2C busses, by setting the SPI mode. All busses operate in an open collector fashion, and **require external pullups**.

## 3.1 Threshold Levels and Supply Voltage

ST/CMOS pins must be used with buses operating from the same voltage as the BL233. Ie if the BL233 is operating from 5V, the I2C bus must run from 5V. ST/CMOS pins have best noise immunity, and are the first choice, especially where cable lengths are longer. *Bus#1,2 are ST/CMOS*

TTL pins have low thresholds. They will work when the I2C bus is at a lower voltage than the BL233. Even if the I2C voltage is 1.8V, and BL233 is operating from 5V, the TTL pins will work. *Bus#3 is TTL*.

In the I2C-2-PC adaptor Bus#3 has a diode clamp to hold the pullup voltages down to the VDD voltage on the I2C connector so it is easy to use with any low voltage device.

## 3.2 Bit Timing

Timing complies with the specs for standard 100kHz I2C. To slow the bus you may load another value into the I2Ctiming byte with the **J** command. see 6.1:Setting Control Register and Bus Timing

## 3.3 SCL Stretch

SCL Stretch is supported. It is implemented on a bit-by-bit basis.

It is tested at the *start* of a cycle, or S or P states.

Why test at the *Start* when the slave asserts stretch at the end of a cycle?

The stretch is asserted by the slave after the ACK, however it does not impact the master until it attempts to begin the next byte/S/P. By testing at the beginning of the next byte, most SCL stretches will have no affect on throughput.

SCL Stretch should be asserted for <10ms. Clock stretch will timeout after approx.  $2^{18}$ /fXtal secs. (17ms @ 14.7MHz). A clock stretch timeout is flagged in the status register.

## 3.4 Four Wire Bus

It is significantly easier to isolate a bus when the transmit and receive are split. A 4 wire logical bus can be used where galvanic isolation is required.

For most applications where SCL stretch is not used, 2 isolators are needed *from* the BL233, and only a single return SDA isolator. In this case a half-split bus can be used. You can use a single IL716 magnetic coupler from NVE<sup>3</sup>.

Note that it is often easier to isolate the RS232 bus. Our I2C2PC adaptor is available in an isolated version.

<sup>&</sup>lt;sup>3</sup> http://www.nve.com/

#### 3.5 Fast Mode

Busses can also be operated with Fast Mode (400k<sup>4</sup>) timing. This improves throughput somewhat when high baud rates are used.

#### 3.6 Multimaster Arbitration

There is no support for multimaster. BL233 assumes it is the only master on the bus. Where multiple masters are desired on a bus, for example in a ATE set, I/O pins can be used to handshake between masters, or to reset/disable the other master when the BL233 wants the bus.

<sup>&</sup>lt;sup>4</sup> The pulse timing is designed to comply with the Philips requirements for Fast Mode. The actual clock frequency is about 200kHz at 14.76MHz fXtal.

## 4 Table 2: Command Character List

| Char   | Command                                |              | Chars      |                                                                   |       |

|--------|----------------------------------------|--------------|------------|-------------------------------------------------------------------|-------|

| O      | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |              | to         |                                                                   |       |

| 0-9    | Hex                                    |              | Follow 1-∞ | lower case <b>a-f</b> are NOT hex                                 |       |

| A-F    | TICA                                   |              | 1-∞        | lower case a-1 are NOT liex                                       |       |

| :      | PauseUntilEOL                          |              |            | Pause execution until EOL char                                    | 5.8   |

|        |                                        |              |            | received. (except in EE, see below)                               |       |

|        |                                        |              |            |                                                                   |       |

|        | ForceReturnToRS232                     |              |            | Execution <i>unconditionally</i> returns to RS232 buffer if in EE |       |

| ;      | ReturnToRS232IfChars                   |              |            | Execution returns to RS232 buffer <i>if</i>                       |       |

| ,      |                                        |              |            | there are chars in buffer, otherwise                              |       |

|        | D.                                     |              |            | continues in EE                                                   |       |

| <      | Return                                 |              | 0          | Execution returns from a macro, either to calling macro or RS232  |       |

|        |                                        |              |            | buffer                                                            |       |

| =      | unused                                 |              |            |                                                                   |       |

| >      | Jump to EE                             |              | 2          | Execution jumps to macro in EE                                    |       |

| 3      | Query Status                           |              | 0          | returns status register                                           | 6.2   |

| 9      | unused                                 |              |            |                                                                   |       |

| G      | Set Bus Number                         | N            | 1-F        | Sets the I2C Bus to use. Will execute                             | 5.6   |

| н      | Hi-speed start                         |              |            | STOP (P) before changing bus. Future Use for HS mode              |       |

| I      | Check Interrupt                        | I            |            | Checks Int pin, and execute Int macro                             | 6.3   |

| -      | Check interrupt                        | 1            |            | regardless of fInterruptEnable                                    | 0.5   |

| J      | Write Control Flags &                  |              |            |                                                                   | 6.1   |

|        | Timing                                 |              |            |                                                                   |       |

| K      | Dalan MMMM ma                          | T            | 4          |                                                                   | 5.7   |

| L      | Delay NNNN ms Set Message Number       | Lnnnn<br>Mnn |            |                                                                   | 7     |

| M<br>N | Nack                                   | IVIIIII      | 0,2        | send nack during special reads                                    | 5.9.2 |

| 0      | Output Direct to Pins                  |              | 1-∞        | write direct to pins and tri-state                                | 8     |

|        | Output Direct to 1 ms                  |              | 1          | registers                                                         |       |

| P      | I2C Stop                               | P            | 0          |                                                                   | 5.2   |

| Q      | Query Direct from Pins                 | Q            | 0          | Reads pins directly                                               | 8     |

| R      | Read nn bytes                          | Rnn          | 2          | Reads NN bytes from previous address (I2C) or SPI, 1 Wire         | 5.5   |

| S      | I2C Start                              | S            | 0-∞        | 100 (100) 01 01 1, 1 11 110                                       | 5.1   |

| T      | Type Char                              | Tnn          | 2-∞        | Types data back                                                   | 6.3   |

| U      | Dump EEProm                            | U            | 0          | Dumps whole EEProm                                                | 11.6  |

| V      | Write EEProm                           | Vaadd        |            | Write eeprom from address aa                                      | 11.5  |

| W      | Write                                  | Wdd          |            | Writes bytes to previous address                                  | 5.5   |

| X      | Software Reset                         | 5A           | -          | "X5A" forces a power on reset                                     | 15    |

| Y      | SPI Mode                               | n            |            | Set SPI Mode. N sets bits to send for                             | 9     |

|        |                                        | 11           |            | next write to do short writes.                                    |       |

| Z      | sleep                                  |              |            |                                                                   | 16    |

| Char         | Command                       | Chars<br>to<br>Follow |                                   |      |

|--------------|-------------------------------|-----------------------|-----------------------------------|------|

|              |                               |                       |                                   |      |

| •            | (fullstop)                    |                       | echo EOL back for formatting      | 12.8 |

| ,            | (comma)                       |                       | echo comma back for formatting    | 12.8 |

|              | (space) ignored               |                       |                                   |      |

| 0x80<br>0xFF | Chars>=0x80 are used as ASCII |                       | Special mode, enabled via fSerial |      |

|              |                               |                       |                                   |      |

## 5 Command Format

The BL233 uses a simple printable Ascii format<sup>5</sup>. Hex<sup>6</sup> characters are used for all data and I2C addresses. Other characters are used as single char commands. Unrecognised chars are generally ignored<sup>7</sup>.

Chars are generally processed and acted on immediately.

The basic form follows that shown in the Philips I2C documentation.

I2C Addresses: Our convention is to write addresses as 8 bit numbers including the R/W bit position. So an EEProm has a base address of 0xA0

## 5.1 A simple I2C Transaction

Consider writing 0xD7 to a Philips PCF8574 8 bit Port. The base address is 0x40. Send:

### S40D7P

[I2C Start][Address:0x40][Data:0xD7][I2C Stop]

The command S sends an I2C Start. P is an I2C Stop, just like the Philips documents. To send a string of 80/81/80.... to the port:

S 40 80 81 80 81 P8

Repeated Start:

S 40 80 81 S 82 S83 P

### 5.2 **Stop**

P returns the I2C bus to the idle state. You should leave the bus stopped when it is idle. Interrupts and other automatic actions need the bus to be stopped, so they don't split an indivisible operation.

When an I2C bus *STOP* fails because SDA remains low, BL233B now sends up to 8 extra SCL pulses to try and clear it automatically. See the I2C Deadlock section to understand this.

## 5.3 Reading I2C

The adaptor looks at bit 0 (R/W bit) of the address byte. If 1, this is a read. To read, set bit 0 of the address eg: read 2 successive bytes from address 0x40

<sup>&</sup>lt;sup>5</sup> Using printable ASCII is easy to understand and debug, and is easily passed through the Internet to a remote BL233.

<sup>&</sup>lt;sup>6</sup> Only upper case A-F are considered hex. Lower case a-f will be ignored or recognised as commands

<sup>&</sup>lt;sup>7</sup> Spaces are always ignored. You may freely use them to make strings more readable (if slower). You can use CR and/or LF if you wish.

<sup>&</sup>lt;sup>8</sup> Spaces and commas will be ignored, and can be used for clarity (but will slow down comms)

#### S4102

[I2C start][Address:0x40 R/W=Read][Number Bytes to read: 02 (0x02)] The adaptor replies with 0x83 both times: 8383[eo1]<sup>9</sup>

Repeated Start:

S407D S4101P

7D[eo1]

[start][write 0x7D][repeated start][read 1 byte][stop] [adaptor returns 1 byte)]

## 5.3.1 Reading an indeterminate number of bytes: Pascal Strings

Due to the way the I2C bus works, (master controls reads), the master has to know how many bytes to read. If the device is returning an indeterminate number, eg a string, then we have a problem.

The BL233 has support for reading pascal style strings. If the *NumberOfBytes* is 0, then it will take the first byte read from the I2C slave, to be the string length.

eg an I2C slave (0x40) has the pascal string "Hi", ie 0x 02 48 49

S4100

4849[eol]

### 5.4 10 Bit Addresses

Carefully study the Philips notes on 10 bit addressing. In short: you write 2 address bytes, so any read is done by a write(2 address bytes), then a read, with only the first address byte.

The R and W commands are particularly useful with 10 bit addresses to reduce traffic.

#### 5.5 R and W: Fast Read/Write Commands

Where you want to read or write to the previous address use R and W<sup>10</sup>. eg instead of **S4083 S4101 S407D P S407E S4101 P**

Using R and W to read and write the previous addresses is much shorter.

S4083 R01 W7D W7E R01 P

10 Bit addresses will be correctly handled.

## 5.6 Selecting the I2C Bus

G selects the I2C Bus. If the bus is not in the stop (P) state, then the adaptor will execute a P before changing the bus.

Busses 1-4 are separate busses. Busses > 4 use the same pins in different ways. It is important to write your code to allow bus numbers to be easily changed to allow for future BL23X chips.

### S4083 G2 S4084 G1

[Write 0x83 to PCF8574 on Bus1][Select Bus 2][Send 84 to another 8574 on Bus2][return to bus 1]

<sup>&</sup>lt;sup>9</sup> [EOL] is the End of Line char. It defaults to LF (0x0A).

<sup>&</sup>lt;sup>10</sup>R & W are also used for SPI operations

Multiple I2C Busses allows you to have more of one type of chip than sub addressing allows. (eg 24 PCF8574's).

**Table 3: I2C Bus Pin Functions**

| Bus# | SDA | SCL | SDA In | SDAOut | SCLIn | SCLOut | CS | Fast |                             |

|------|-----|-----|--------|--------|-------|--------|----|------|-----------------------------|

| 1    | 18  | 17  |        |        |       |        |    |      | Bus 1 Standard I2C          |

| 2    | 2   | 1   |        |        |       |        | 3  |      | Bus 2 Standard I2C          |

| 3    | 13  | 12  |        |        |       |        | 11 |      | Bus 3 Standard I2C          |

| 4    | 11  | 3   |        |        |       |        |    |      | Bus 4 Standard I2C          |

| 5    | 18  | 17  |        |        |       |        |    | #1   | Bus 1 Fast I2C              |

| 6    | 2   | 1   |        |        |       |        | 3  | #2   | Bus 2 Fast I2C              |

| 7    | 13  | 12  |        |        |       |        | 11 | #3   | Bus 3 Fast I2C              |

| 8    |     |     | 2      | 13     | 1     | 12     |    |      | Full split, Bus2 is inputs, |

|      |     |     |        |        |       |        |    |      | Bus 3 outputs               |

| 9    |     | 1   | 3      | 2      |       |        |    |      | Bus 2 Half Split            |

| Α    |     | 12  | 11     | 13     |       |        |    |      | Bus 3 Half Split            |

| В    |     |     |        |        |       |        |    |      |                             |

| C    | 18  |     |        | 17     |       |        |    |      | 1Wire#1                     |

| D    | 3   |     |        |        |       |        |    |      | 1Wire#2                     |

| Е    | 13  |     |        | 12     |       |        |    |      | 1Wire#3                     |

| F    | 11  |     |        |        |       |        |    |      | 1Wire#4                     |

|      |     |     |        |        |       |        |    |      |                             |

Some bus numbers use some or all of the same pins as another bus.

## 5.7 Delaying

To output a pulse we can use Delay (L). Delay is up to 65535 milliseconds<sup>11</sup>. **\$4001 L0400 W00**

[Set bit0 of PCF8574 HI][Delay 0x400ms ie ~1 sec][Set bit 0 LO]

## 5.8 Pause Command for Timing Critical Sequences

':' (colon) pauses execution until an EOL char (LF) is received. Chars after the ':' are stored in the buffer, but not processed until an EOL char is received. This ensures that the sequence of operations between ':' and EOL will always take the same time, irrespective of baud rate or undefined computer delays.

## :S4001 L0001 W00 [eol]

[pulse bit0 high for 1ms]

(hint: using ":" can make it easier to watch data sequences on a oscilloscope) Obviously the string between ':' and EOL must fit in the RX buffer.

An alternative for timing critical sequences is to put them in the EEPROM as a macro.

## 5.9 I2C Acknowledge

Read the Philips I2C documentation closely.

At the end of each byte transfer there is an acknowledge.

<sup>&</sup>lt;sup>11</sup> Timer tick rate can be changed in EEProm

## 5.9.1 Writing

When writing the *slave* generates ACK. (pulls the bus LOW) If the slave does not ack, then either

- It is not present

- It is not ready or prepared to accept any more data

Most hardware designs and hardware type I2C slaves are deterministic.

- The device is always present if it was present once.

- Most devices always accept the number of bytes you will try to send

For this reason the default is to ignore nack. You can check the result of the last writes by QueryStatus (?). This is an easy way to check the bus for I2C devices at power on. *Nack* is cleared at each START. Note that "?" can be put between data bytes.

Two fControl flags offer more sophisticated nack handling

| fC <sub>0</sub> | ntrol |              |                                                                                                                                                         |

|-----------------|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit             | Rst   | Name         | Description                                                                                                                                             |

| 3               | 1     | WrIgnoreNack | makes I2C write routines ignore nack. The interface                                                                                                     |

|                 |       | (default)    | will continue to write bytes to the bus even after a                                                                                                    |

|                 |       |              | nack.                                                                                                                                                   |

|                 |       |              | Writes halt when nack occurs. Subsequent bytes are ignored. Writes "N" back to host                                                                     |

| 2               | 0     | RdBlockAck   | nack won't be sent when last byte is read                                                                                                               |

| 1               | 0     | AckWrites    | writes K/N as each byte written to I2C is/not acknowledged by the slave "K" nack'd OK "N" failed to nack Useful for debugging. Clears Nack at each byte |

## 5.9.2 Reading

When reading from a slave the nack is generated by the master (BL233) as each byte is received.

The I2C Bus requires that after receiving the last byte a master doesn't nack. This signals end-of-data to the slave.

The BL233 handles this automatically.

However you might wish to read a large number of bytes from a slave (eg >255), or read as a series of shorter blocks, without signalling end-of-data to the slave.

In this case you can set the flag fControlReadBlockAck. In this case all reads will be ack'd, and you must take care to nack the last read yourself with an N command before the final read. Note that you can read multiple blocks by sending a series of byte counts.

<sup>&</sup>quot;N" makes the last read NOT ack, thus signalling the end to the slave.

#### S41 04 04 04 N 04

[read 16 bytes from 8574. Reads 4 byte blocks with ack 3 times. N makes last byte nack to end transfer]

You *must* use the **N** command. Otherwise it may be impossible to send a STOP. This will happen if the first bit of the next byte is 0. In this case the slave will be asserting SDA=0, and the master will be unable to send stop.

Note that the BL233B's ForceStop mode will send extra clock pulses to force a stop onto the bus regardless. However this is slow, and is doing extra operations to the slave (depending on the data).

## 6 Status and Control Registers

|     | fControl (write) |                    |                                             |  |  |  |  |

|-----|------------------|--------------------|---------------------------------------------|--|--|--|--|

| Bit | Default          | Name               | Description                                 |  |  |  |  |

| 7   | 0                | SuppressEOL        | suppress EOL following data reads           |  |  |  |  |

| 6   | 0                | EmitWriteResult    | returns data read as byte written (see SPI) |  |  |  |  |

| 5   | 0                | RxWatchdogEnable   | enables the watchdog on rx chars            |  |  |  |  |

| 4   | 0                | InterruptEnable    | enables interrupt response                  |  |  |  |  |

| 3   | 1                | WrIgnoreNack       | makes I2C write routines ignore nack        |  |  |  |  |

| 2   | 0                | RdBlockAck         | nack won't be sent when last byte is read   |  |  |  |  |

| 1   | 0                | ShowAck            | returns "K" or "N" as each byte written to  |  |  |  |  |

|     |                  |                    | I2C is/not acknowledged by the slave        |  |  |  |  |

| 0   | 0                | MessageNumsEnabled | enables return of message numbers           |  |  |  |  |

|     | fStatus (read) |         |                   |                                               |  |  |  |

|-----|----------------|---------|-------------------|-----------------------------------------------|--|--|--|

| Bit |                | Default | Name              | Description                                   |  |  |  |

| 7   |                |         |                   |                                               |  |  |  |

| 6   |                |         | 1WirePresence     | if a presence pulse exists during reset       |  |  |  |

| 5   |                |         | 1WireInterrupt    | A device signals INT during reset pulse       |  |  |  |

| 4   |                |         | Int               | Current state of Interrupt pin (0=active int) |  |  |  |

| 3   | *              |         | TimerTimedOut     |                                               |  |  |  |

| 2   | *              |         | FifoOverflow      | Either RX or TX fifo overflowed               |  |  |  |

| 1   | *              |         | ClkStretchTimeout | I2C timed out waiting for SCL to go Hi        |  |  |  |

| 0   |                |         | Nack              | result of last I2C Nack                       |  |  |  |

## 6.1 Setting Control Register and Bus Timing

To set the control register only.

**J** [control register]

To change the I2C Bus timing. 0 is fastest, 255 is very slow.

**J** [control register] [I2C Timing]

eg Write only fControl to enable interrupts (and WriteIgnoreNack)

J14

eg To Enable Ints and set I2Ctiming to 15

J140F

<sup>\*</sup> Cleared by reading status register

Note: You cannot read back the control register or timing values.

## 6.1.1 Bus Timing Value

Bit/Bus timing is set by the **J** command. The Timing value is 0 - 0xFF. Experiment to see what the timing is.

Different bus modes (eg normal, fast, 1-wire etc) have different bit timing for the same value. The timing is also non linear at small values eg 0,1,2 can be quite different.

If you use different timing for different buses, then you have to change it when you change bus#, as the timing value is global to all buses.

## 6.2 Querying Status Register

? returns the status register. This is most commonly used to

- check NACK to see if the last write was acknowledged by the slave.

- check state of the interrupt pin (0 is INT)

- check flags after a 1Wire reset

"?" does not interfere with the command currently being executed, so you can put it in the middle of a series of bytes being written, or between reads.

## 6.3 Interrupt Pin

- You can check the interrupt pin by reading the status register with? at any time

- I command checks the interrupt pin, and executes interrupt macro in EEProm, regardless of the state of the fInterruptEnable. The address of the interrupt macro is set in the IRQ1Vector in EEProm.

- If fInterruptEnable is set, then interrupt pin is checked at each *Stop* (**P**) command, and the interrupt macro executed if it is low.

The default interrupt routine just types "i" back.

To enable interrupts set the InterruptEnable bit of fControl register eg.

J18

[enable interrupts]

J08

[disable interrupts]

If you want to wait for interrupts, then a simple macro in eeprom will loop waiting for interrupts.

I;>60

(start is at location 60)[Check Ints][return if the PC sends a char][jump to 10 (start)] Change the interrupt macro to be

T69:

[type "I"][leave EEProm]

Then to run the "wait for interrupt" macro >60

Now when INT goes low, a single "i" is typed. (with the original macro "T69<" it returns, and prints "i" repeatedly while INT is low)

The Interrupt macro, and the Interrupt Vector are in EEProm. See 11 for more details.

#### 6.4 Return a Char

T types any chars back to the PC. It is very useful for formatting and synchronising data.

#### S407D T563D R01

V=7D[eol]

[set 8574 to 0x7D][Type "V=" back to PC][reads 8574: 0x7D]

- make return data more readable or parseable

- you don't have to wait for a specific reply

(see also: EOL, Separator Chars, and Data Formatting, 12.8below)

The start-up welcome "Hi I2Cad VXXX" message works this way.

Remember that the I2C adaptor is going to return upper-case hex chars, and a few special upper case chars in certain cases (eg N,K)

Type different chars or lower case chars back, then it is very easy to separate them out of the data stream.

## 7 Message Numbers

Message Numbers provide a way of dealing with latency. The message number is 8 bits

Without message numbers it can be difficult to pair up commands and returned data, especially when long latencies are involved. eg

S407D R01 L0100 R01

7D[eol]7D[eol]

If we turn on message numbers, and set the message number to 0x05 **S407D M05 R01 R01 R01**

057D[eo1]067D[eo1]077D[eo1]

Now it is easy to pair each query to its reply.

Message numbers are 8 bits, autoincrement, and wrap around from 0xFF -> 0

Message numbers are enabled by **fControlMessageNumsEnabled**, or by the first occurrence of an M.

M without data will zero the message number.

S407D M05 R01 M R01 R01 057D[eol]007D[eol]017D[eol]

Another way to synchronise, is to use "T" to type specific chars back.

After sending **M** the only way to disable messge numbers is by writing the control register.

## 8 Direct Pin I/O

The BL233 makes a great 8 bit I/O port for a PC! You can read and write 8 pins directly.

## 8.1 Reading Pins

'Q' queries the actual pin state. In the I2C-2-PC adaptor there are pullup resistors on the pins so they idle high.

One use for  $\mathbf{Q}$  is checking for bus faults and the deadlock condition, after an I2C Stop.

The INT pin can be read using the ? status command.

## 8.2 Writing Pins

The 'O' output command can be used to write to the output pins, and the data direction registers. The bit number of each pin is given in 2 Table 1: BL233 Pinout Description. Before you can use a pin as an output (or CS for SPI) you must set its tristate bit to 0.

Expects sequence of **O** Data, Tristate, Data, Tristate..... You can write 1 or more bytes in this sequence

#### O OF OE 5A

[write][Data=0x0F][tristate=0x0E][Data=5F]

Inputs have tristate register bits = '1'. Outputs have tristate bits=0.

Once you have set the tristate register you can simply write to the data register: O 1F O FF

You have to take great care using direct pin I/O when you are also using serial busses, as the bus functions of the chip expect the registers to be set up a certain way. All bus pins have DATA bits=0, TRIS bits=1.

If you are only using the two CS pins see below.

To restore the idle condition send

O 00 FF.

CS pins on the I2C-2-PC will idle high as they have pullups.

## 8.2.1 Pin Timing

Writes and reads to the pins are done with bits 0-4 changing first, and bits 3-7  $\sim$ 1  $\mu$ s later.

## 9 SPI

8 bit bytes are written using SCL and SDA. Data is shifted out MSB first, (as is I2C). The bus must be in *STOP* before using SPI write. The SPI **strobe** or **CS** pin function is done using Direct I/O sec 8 above.

SPI Mode is entered by the "Y" command. SPI mode is exited by "Y0"

## P Y W 01 02 03

[I2C Stop][SPI Mode] [write 0x01,0x02,0x03]

#### P Y R 03

[I2C Stop][SPI read 3 bytes]

#### P Y W 01 02 03

[I2C Stop][SPI write 0x01,0x02,0x03]

### 9.1 CS/Strobe Pins

These are driven by simple bit bashing using the direct I/O command "O" above. Don't forget that the direction/tristate byte must be set before writing data bytes. First initialise I2C2PC to use CS#2,3 as outputs. (only need to do this once)

#### P O 30 CF

[I2C Stop] [Set Bus2,3 CS to outputs and high]

Then we can write to the port.

### O 00 Y W 03 04 O 10

[Set bit 4 (Bus#2 CS) LOW][SPI write 2 bytes (0x03,0x04)][Set bit 4 (Bus#2 CS) HI]

#### 9.1.1 CS Pins and commands for I2C-2-PC

The I2C-2-PC uses Buses 2 & 3 for SPI transfers if the jumpers are changed to the CS position. This makes pin 5 of the connector CS.

Before using the CS pins you need to write 0 into the appropriate TRISTATE bits.

|                   | Pin# | Bit | TRIS  | Initalise | <i>CS</i> =1 | CS=0 |

|-------------------|------|-----|-------|-----------|--------------|------|

|                   |      | #   | Value | (CS=1)    |              |      |

| CS on Bus #2 Only | 3    | 4   | EF    | O 10 EF   | O 10         |      |

| CS on Bus #3 Only | 11   | 5   | DF    | O 20 DF   | O 20         |      |

| CS on Bus #2 & #3 |      |     | CF    | O 30 CF   | O 30         | O 00 |

|                   |      |     |       |           |              |      |

So if you are using I2C2PC and want to use CS 2,3 then use these commands to initialise and control the CS pins.

|                    | CS2 | CS3 | Command |

|--------------------|-----|-----|---------|

| Initialise CS pins | 1   | 1   | O03CF   |

| Change CS          | 0   | 0   | 000     |

| Change CS          | 1   | 0   | 010     |

| Change CS          | 0   | 1   | 020     |

| Change CS          | 1   | 1   | 030     |

Note that *any* unused lines can operate as additional CS pins. This means unused SDA and SCL pins. For example Bus 2 might be used for SDA, SCL, CS1, while Bus 3 is used as CS2, CS3, CS4

### 9.2 The Data Pins SDA vs MOSI / MISO

I2C uses a common data pin for in and out (SDA). Many SPI chips have separate pins, often called MISO (master in, slave out) and MOSI (master out, slave in).

Even though there are separate in and out pins, many SPI devices have tri-state outputs on the MISO pin. These are only enabled during that part of the transfer when data is being read out of the slave. In this case, the MISO and MOSI pins can simply be connected together, and connected to the SDA pin of the BL233. (It is obvious that spi chips have tristate outputs, or else only a single slave could connect to the MISO line)

However some devices really do require separate pins. In this case you use the half-split bus. (command G9 or GA). This gives you separate SDA\_In (MISO) and SDA\_Out (MOSI) pins.

If you are using the I2C-2-PC then these are the split data pins that are possible:

| Bus#      | Pin# | Levels | G8      | <b>G9</b> | <b>G</b> A |

|-----------|------|--------|---------|-----------|------------|

| Bus 2 SDA | 1    |        | SDA Out | SDA Out   | CS2        |

|           |      |        | MISO    | MOSI      |            |

| Bus 2 SCL | 4    |        | SCL     | SCL       | CS3        |

| Bus 2     | 5    | CMOS   | CS1     | SDA In/   | CS1        |

| CS/IRQ    |      |        |         |           |            |

|           |      |        |         |           |            |

| Bus 3 SDA | 1    | TTL    | SDA In  | CS2       | SDA Out    |

|           |      |        | MOSI    |           | MOSI       |

| Bus 3 SCL | 4    |        | unused  | CS3       | SCL        |

| Bus 3     | 5    |        | CS2     | CS1       | SDA In     |

| CS/IRQ    |      |        |         |           | MISO       |

#### 9.3 Short Data

Unlike I2C, SPI can have any data length. You can short transfer by specifying the bit count after Y as a single hex digit. This only shortens the next byte. Subsequent transfers will be 8 bits. Data is in the least significant bits of the byte, and data read will have 0 in the unused bits.

#### Y W 5A Y2 W 03 AA Y2 R 02

[SPI][write byte 0x5A][Set for 2 bits][Write 2 bits 0x3][write fullbyte 0xAA][read 2 bits, then 1 full byte]

Bit count=0 exits SPI mode.

Bit count 8-15 is for bidirectional mode below.

Note you can write directly after the Yn command eg

#### Y2 03 AA 55

[write 2 bits (0x03), then full bytes 0xAA, 0x55]

## 9.4 Bidirectional (simultaeneous) Write/Read

Some SPI and 1Wire operations need to read in the data pin as data is written out.

This is supported by the fControl bit fControlEmitWriteResult.

To enter this mode use "Y" with bit count>=8

To exit the mode use "Y" with no bit count.

For each byte written, a byte (2 hex digits) is returned.

Alternatively you can write *fControl* directly. Note that changing the bus will clear this bit

Normally you would be using one of the split buses for this.

## 9.5 SPI Clock Polarity

BL233 does not change the data and clock at the same time. So it will work writing data to both rising and falling edge clocked devices. There is more timing margin at the rising edge, so this is preferred.

Read data is sampled when SCL is Hi, just before the falling edge.

SCL idles LO between transfers.

#### 9.6 M5451

The M5451 devices do not use a CS or STB line. They take 36 bits data, the first bit is 1. To reset/synchronise them after power on write 5 bytes of 00.

To write to them it is fastest and easiest to send 5 bytes of data. The first data bit should be one, and all trailing unused bits must be 0.

Only one M5451 can be connected to each bus.

If using 7 segment displays with an M5451, we recommend the BL301 I2C Versatile Display Driver. It handles the 7 segment decoding and bit re-ordering for you, and connects multiple M5451's to a single I2C bus.

## 10 1Wire Bus

The BL233 has support for Dallas 1 Wire bus, using the standard timing.

- 1Wire busses are selected by bus "G" command, followed by a start

- Start sends bus reset, and samples the presence and interrupt responses

- Write and Read do data transfers

- short bit count transfers and bidirectional Wr/Rd's can be done with the "Y" command as per SPI. This is useful for searching for unknown devices.

Eg to read a DS2401 serial number

### GC S ? W33 R04

[Select 1 wire bus#1 (bus #C)][Start(reset)][Get status to check presence][ReadRom Command][Read 4 bytes of rom data]

Since Start can be followed immediately by write data, a shorter version is:

#### GC S 33 R04

[Select 1 wire bus#1 ][Start][ReadRom command][read 4 bytes]

The 1Wire Reset (Start) checks for interrupts<sup>12</sup>, and presence of a chip. Read the fStatus ("?") to check these flags. If you are using an iButton application where it is possible to short the bus, you can directly query the bus pin with the "Q" command, if interrupt and presence are both true.

#### 10.1 Pins

1Wire uses a single open collector I/O pin, and a 1k5 pullup resistor. However we also have a second output-only pin on some buses. This allows for easy galvanic isolation, or for improved bus driving hardware. For a simple bus, you can just use the SDA pin, and ignore SDA OUT

#### 10.2 Software

You can easily use BL233 with the Dallas "Open Source SDK" for high level 1Wire software. BL233 provides support for byte-read, byte-write, N-bit read/write, "touch" (write & read). With these you can get complete 1 wire functionality.

## 11 EEProm Memory

The 128 Bytes of EEProm contains:

- Stored Settings

- Vectors

- Macros

Note that these are mostly initialisation values loaded at reset, and may not change or reflect the present value or have any effect until reset.

## 11.1 Table 4: EEProm Memory Map

| Address | ~Add | Register   | Description                                 | see  |

|---------|------|------------|---------------------------------------------|------|

| 0xF7    | 08   | fSerial    | RS232 Control Register                      | 12.3 |

| 0xF8    | 07   | Baud_Div   | Baud rate divisor reset value               | 12.4 |

| 0xF9    | 06   | TimerDivL  | <i>Low</i> byte of timer divisor (TimerDiv) | 13.1 |

| 0xFA    | 05   | TimerDivH  | <i>Hi</i> byte of timer divisor             | 13.1 |

| 0xFB    | 04   | fControl   | Control Register                            | 6    |

| 0xFE    | 01   | IRQ1Vector | Macro address for interrupt                 | 6.3  |

<sup>&</sup>lt;sup>12</sup> Note we mean 1wire interrupts, which are signalled by devices stretching the 1wire reset pulse. Not the INT pin that supports the I2C bus

| Address | ~Add | Register   | Description                                               | see |

|---------|------|------------|-----------------------------------------------------------|-----|

| 0xFF    | 00   | Watchdog   | Macro address for watchdog                                | 14  |

|         |      | Vector     | _                                                         |     |

| 0x00    | FF   | Base / POR | First macro instruction. Power-On jumps to this location. |     |

|         |      |            |                                                           |     |

|         |      |            |                                                           |     |

| 0x76    |      | end        | Generally contains a return char "<"                      |     |

#### 11.2 Macros

Macros are stored command chars.

- Commands to execute at power on (see 15)

- Commands to execute when Interrupt is detected

- Commands to execute when there is a watchdog timeout

- macros to speed up common tasks

- very simple "programs" for autonomous actions

## 11.3 A Macro for combined 8 switches + 8 Leds board

This board uses (you guessed it) an 8574. The 8574 is a open-drain driver. We can connect switches across the drivers, and read the switches if we momentarily turn the LEDs off (write 1's)

#### S40FF R01 W <

[write 0xFF to turn leds off][read 1 byte][start write][return] we now expect the LED data to follow.

To use the macro:

#### >20 00 P

[goto macro][new led data][stop]

## 11.4 A simple "program"

This is a simple data-logging application. It reads the 4 A-D channels of a PCF8591, and 8 switches with an 8574, 4 times a second, and streams the data to a PC<sup>13</sup>, that captures it with a terminal program<sup>14</sup>.

start location is 0x10

## S9104 S4101 P L00F9 ; >10

[read 4 a-d][read 8574][delay 249ms][return if the PC sends a char][jump to start]

## 11.5 Writing the EEProm

To prevent inadvertent writes to the EEProm, the start address is sent twice. First normally, then inverted. If they don't match, the whole operation is aborted. The format is V[address][not addr][byte1][byte2].....

<sup>&</sup>lt;sup>13</sup> You could use a TI or HP graphing calculator too.

<sup>&</sup>lt;sup>14</sup> REALTERM.EXE from http://realterm.sourceforge.net

Address 0 is the Base / POR location. So to write F1,01,11 to the POR location:

## V00FF F1 01 11

Each byte written takes 10ms. You need to either send data slowly enough, or in small packets eg 8 locations to avoid overflowing the buffer.

Most settings will only change after a reset.

The EEProm write command is intended for configuration, rather than routine use. You must check that vital data is correct. In particular if the serial parameters are wrong, you will be unable to regain control after the next reset.

(hint: to find the hex for the char string you want to put in EEProm, set Realterm's display mode to hex+ascii, half-duplex. Now type the string, and you will see the hex.)

## 11.5.1 Write Protecting the EEProm

If fSerialEEWriteProtect is set, further writes to EEProm are blocked unless in

## 11.6 Dumping the EEProm

U will dump all 128 bytes of EEProm in the order shown in Table 4: EEProm Memory Map. ie the first byte is fSerial, not Base/POR

#### 12 Serial Comms

Note: Changes to fSerial and Baud Rate will only take effect after a reset, either power-on or software.

Default is **57,600 Baud N81** with a **14.7456MHz** crystal.RTS/CTS handshaking is recommended.

#### 12.1 Data Format

- 8 bits

- No parity

- 1 stop bit

Data format cannot be changed.

#### 12.1.1 HiCharsAsAscii

The BL233 uses two hex digits to represent each single data byte. Sometimes, such as when sending long ASCII strings to displays, this is a significant overhead. When the *HiCharsAsAscii* flag is set, any chars with bit 7 set, will be used as ascii chars with bit 7 clear.

Eg to send the string "Hi" using the T command

## T[0xC8][0xC9]

ie oxC8=0x48+0x80. This is 3 chars, instead of the normal 5 chars, so long strings will be much shorter.

**T4849**

## 12.2 Handshaking

RTS/CTS hardware handshaking is supported. It is controlled by bit fSerial\_UseRTS. CTS will always be output, regardless of *UseRTS*. RTS is ignored by default: (See errata)

XON/XOFF is available to supplement CTS for controlling the flow of data *from* the PC. When XON/XOFF is enabled, CTS is still asserted. Sending of the XON/XOFF chars will always ignore the RTS pin.

The BL233 ignores XON/XOFF characters – they are only used to control the flow of data *from* the PC.

It is recommended that you *only* use XON/XOFF where handshaking lines are not available. It has extra overhead, and is not as reliable a technique as RTS/CTS.

## 12.3 Table 5: Serial Initalisation Registers in EEProm

|         | bit 7   | bit 6       | bit5    | bit4 | bit 3 | bit 2  | bit 1  | bit 0   |  |

|---------|---------|-------------|---------|------|-------|--------|--------|---------|--|

| fSerial | EEWr    | Enable      | HiChars |      |       | UseXon | UseRTS | Baud    |  |

| 1501141 | Prot.   | Sleep       | AsAscii |      |       |        |        | Rate HI |  |

| BaudDiv | Baud Ra | ate Divisor |         |      |       |        |        |         |  |

|         |         |             |         |      |       |        |        |         |  |

### 12.4 Baud Rate

Default is 57,600 Baud N81 with a 14.7456MHz crystal.RTS/CTS handshaking is recommended.

The baud rate is set by writing the ee\_BaudDiv and ee\_fSerial locations in EEProm. The changes will become active when the part is next reset.

if BaudRateHi = 1:

$$BaudRate = \frac{Fxtal}{16 \times (BaudDiv + 1)}$$

if BaudRateHi = 0:  $BaudRate = \frac{Fxtal}{64 \times (BaudDiv + 1)}$

| BaudDiv Values for other Baud Rates (14.7456MHz) |      |      |       |       |       |      |      |  |  |

|--------------------------------------------------|------|------|-------|-------|-------|------|------|--|--|

| BaudDiv: 0x                                      | 03   | 07   | 0F    | 17    | 2F    | 5F   | BF   |  |  |

| Baud Hi                                          | 230k | 115K | 57.6k | 38.4k | 19.2k | 9600 | 4800 |  |  |

| Baud Lo                                          |      |      |       | 9600  | 4800  | 2400 | 1200 |  |  |

Baud rates can be calculated at other crystal frequencies from:

BaudRate HI= Fxtal/(16(N+1))

BaudRate Lo= Fxtal/(64(N+1))

For example to change the baud rate to 9600,

#### V F807 5F

[write eeprom][address, ~address][BaudDiv=0x5F]

Changes are active from the next power on, not immediately

## 12.4.1 Special Pins Mode and Baud Rate Changing Problems

As you can cock the baud rate up, and be left with an unusable chip, we have

provided a special mode where the baud rate and fSerial are in their factory state. To enter SPM, force Pins 1,2,17,18, and 6 to 0V, during and 500ms after reset / power on. Now you can change the EEProm values.

If you leave unused pins floating, the the part may be in special pins mode during start up. If this happens the baud rate will remain at default, even though you have successfully changed the eeprom values. Unused pins should be pulled up.

## 12.5 Max Baud Rate and Speed

The BL233 can have baud rates as high as 921kbd. However it cannot process commands at this rate. Different commands take differing amounts of time to execute, and so you should experiment to find the optimal rate for your application. It is likely to have an appropriate throughput for 115kbd.

Where speed is an issue, make use of macros stored in EE to reduce the serial traffic.

## 12.5.1 PC Serial Port Latency

While Windows PC's, USB devices, and anything running over the internet, have high data throughput (bytes per second), they have long latencies or transit times. On a Windows PC that can send 10,000 bytes/sec, it may take as long as 300ms for a single char to loop back.

#### 12.5.2 RS232 Drivers

At high baud rates (20k +) you need to pay attention to the RS232 Drivers. Driver IC's vary in their ability to drive longer cables at high speed. Variants, eg xxxE parts can have different speeds. Different manufacturers versions of the same part have different speeds. Also beware that at the PC end, some serial ports eg older laptops, may use low power drivers that are rated to 20k only.

#### 12.6 Serial Buffer Size

It is best to keep command strings within the buffer. When reading a port, avoid reading more chars than will fit in the buffer.

- RXD Buffer: 48 Chars from PC

- TXD Buffer: 80 Chars to PC (each byte read will be 2 hex chars in the buffer)

## 12.7 USB

The usb has a drawback. Data is passed in 1ms frames. This means that there is a minimum 1ms turnaround for even a single char. Structure your data so that you send as many commands as possible before your program requires a response.

## 12.8 EOL, Separator Chars, and Data Formatting

EOL (LF 0x0A by default) is sent after any data to separate commands. eg S41 R01 SA1 R02 P L0100 S41 R01 S42 R02 P 01[eol]

FE02[eo1] 01[eo1]

### FE02[eo1]

This is convenient for program control, but may be awkward where you want to capture files with tables of data.

fControlSuppressEOL allows you to suppress the automatic EOL character. Two shortcuts are available: Comma is echoed back and fullstop returns EOL.

#### **J88**

[set Control to suppress EOL char]

S41 R01, SA1 R02 P. L0100 S41 R01, S42 R02 P.

01, FE02[eo1]

01, FE02[eo1]

You can explicitly insert any char using the T command. eg TAB, CR etc

The unix/mac utility TR (available on the PC in UnixUtils package) is useful for translating formatting chars in files eg commas to spaces, LF to CR etc. fControlSuppressEOL will affect all operations except dUmp, which always has an EOL.

## 13 Oscillator

The standard oscillator frequency is 14.7456MHz. This permits standard baud rates as high as 921kbd.

As the BL233 is much faster than many applications will require, you can change the crystal for a lower frequency. This will allow operation at lower voltages, lower supply current, and reduced EMI.

Both BaudDivisor and TimerDivisor can be set in EEProm.

The max oscillator frequency is 20MHz. The I2C Bus timing is set for *Standard Mode* at 14.74MHz

#### 13.1 Timer

The timer ticks run at 1ms with a 14.7456MHz crystal. You can change the timer rate using the 16 bit EEProm register TimerDiv<sup>15</sup>.

$$TimerDiv = round \left( \frac{Fxtal}{4 \times TimerRate} \right)$$

| Timer Rates @ 14.7456MHz |        |        |                     |        |         |         |  |  |  |

|--------------------------|--------|--------|---------------------|--------|---------|---------|--|--|--|

| Timer Div                | 0x0E66 | 0x01CC | 0x3840              | 0x4800 | 0x9000  | 0xFFFF  |  |  |  |

| Timer                    | 1ms    | 2ms    | 256Hz <sup>16</sup> | 5ms    | 10ms    | 17.8ms  |  |  |  |

| Watchdog                 | 66s    | 2m 11s | 4m 15s              | 5m 28s | 10m 55s | 19m 25s |  |  |  |

## 13.2 1-Wire Timing

1-Wire bus timing cannot be adjusted and will scale with the clock frequency.

<sup>&</sup>lt;sup>15</sup> numbers are stored low byte first in EEProm

<sup>&</sup>lt;sup>16</sup> High byte if TimerDiv will be in secs at 256Hz Timer rate

## 14 Watchdog

The chip has a watchdog function that is used to monitor correct functioning of the host computer. A typical use might be to force a hardware reset of the host PC, or to force outputs into a safe idle state if the controlling PC crashes.

The watchdog period is fixed at approx  $2^{16}$  timer ticks, normally ~65secs.

Each time a character is received from the host, the watchdog is restarted. After 2<sup>16</sup> ticks without a character received, a watchdog event can be generated.

If the watchdog vector is not 0, and the RxWatchdogEnable is set, then execution jumps *immediately* to the watchdog macro. The current character will be processed, then the next char is fetched from the watchdog location.

The RxWatchdogEnable flag is cleared, and any pending chars in the input fifo that are waiting for an EOL char, are unblocked.

You need to bear in mind that bus transactions may be left half completed, and so you may need to use **P,S,G** or other commands before using the I2C bus.

The default Watchdog macro just types "w"

## 14.1 Uses

- Use a relay board to reset the PC if the flow of chars stops.

- Attach to a PC on the far side of a router getting chars through the network. Turns the router power off for a few seconds when the flo of chars stops.

## 15 Reset

**X5A** causes the part to do a power-on-initialise. (5A is required to prevent inadvertent operation).

- any characters following the X5A will be flushed from the buffer and lost.

- reset will take several milliseconds, so you must pause before sending further commands

- The POR macro will execute at power on and X5A reset.

## 15.1 Low Voltage Reset

**BL233B** no longer has low voltage reset, and will operate to <3V. 4V Reset is still available as a special factory option if required.

### 15.2 Power On Reset Macro

At power on or reset execution begins at 0 in the eeprom. The factory default macro types "HI I2C v118" using the **T** command.

*Caution:* If you write a macro that has an endless loop as the POR/Reset macro, you will be unable to recover the chip.

## 16 Sleep Mode

not implemented

Due to the perils of putting the part to sleep this function is not enabled. Contact the factory if your application needs this function.

If *fSerial.EnableSleep* is set, **Z** will put the part to sleep. (by default sleep is disabled) It will wake on pin change. This could be from an I2C interrupt, or by the PC toggling RTS. If you need the PC to wake up the via RXD, connect RXD to SDA4 through a resistor.

You need to allow 10ms for wakeup from sleep.

If you are waking it with the RXD line you need to be aware of the potential for waking up part way through the char used to wake it. For this reason 0xFF is recommended as the wakeup char.

## 16.1 Pause and Sleep

When the Sleep bit is set, the clock oscillator is stopped and the BL233 current consumption drops.

The BL233 is unable to receive any further chars, and you could expect chars to be garbled if they occur during transition times.

Execution will resume after some delay depending on how the part exits Sleep.

During pause command execution is paused, but there is no change in current consumption or oscillator. The part will exit pause immediately. Timing during pause is accurate.

## 17 I2C Bus Connectors and Pinouts

We use this pinout, and recommend that you do also. More details, and connector part#'s, suppliers etc see: http://www.i2cchip.com/i2c connector.html

| Pin# | 6 Way | 4 Way |                                                 |

|------|-------|-------|-------------------------------------------------|

| 1    | SDA   | SDA   |                                                 |

| 2    | +5    | +5    |                                                 |

| 3    | Gnd   | Gnd   |                                                 |

| 4    | SCL   | SCL   |                                                 |

| 5    | INT   |       | Interrupt input (active low). Can be used as CS |

|      |       |       | when being used for an SPI bus.                 |

| 6    | VAux  |       | Aux supply (eg 12V), or other uses.             |

## 18 I2C Bus Deadlock

A known issue with the I2C Bus is the possibility of a deadlock. SMBUS has addressed this with a requirement for an automatic timeout. However the possible causes of bus deadlocks are seldom explained.

I2C relies on the two special conditions sent by the master: *START* and *STOP*, where SDA changes state while SCL is high.

If (for some reason) a slave holds SDA low, then the master is unable to send the STOP condition, and the bus state cannot be reset. In some situations the bus can

remain busy indefinitely, in others there will be an indeterminate number of faulty operations performed until the bus comes free.

We know of two situations where this can arise. Both involve reading a slave, and the slave outputting a 0 data bit.

## 18.1 Added/Dropped Clock Pulses

In the first case a clock pulse is added or dropped, (eg by noise) during a transfer. Now we find that when the master thinks that it is at the end of a byte, the slave is still outputting a data bit. If this data bit is a 0, then SDA is held low, and *STOP* cannot be sent.

This situation could arise either from noise, or perhaps from the master software being interrupted part way through a transfer.

In the second case a programming error is too blame. The master does not send NACK (ie leave the NACK bit=1) at the end of a byte read from a slave. At the end of the clock pulse for the NACK bit, the slave will begin outputting the next date bit. If this is 0, then the master will be unable to raise SDA.

### 18.2 Failure to send NACK after last read

Note that both these are dependent on the data in the slave. If the slave does not have a 0 in the correct bit, then there will be no problem. This helps to make the problems more elusive.

Note that normally the BL233 takes care of sending the NACK correctly. Only if you override the NACK control bit will you have to watch this.

## 18.3 BL233B Automatic STOP Recovery

The BL233B checks SDA after a *STOP*. If SDA is still low, then it will clock the SCL line up to 9 more times to try and clear the deadlock.

### 18.4 Demonstrating the Problem

Connect a PCF8574 to I2Cbus1

### 18.4.1 Extra Clock Pulse

J0C

[set mode to not send ack after reads. this gets us halfway through a read operation] : **S4000S4101**

[write all 0's to a PCF8574. Now read back 1 byte. BL233 sends ack, so slave expects another read to follow]

#### :O 00FE 00FF 00FE

[this sends an extraneous clock pulse, reading the next data bit (a 0) from the 8574]

[STOP fails because 8574 is holding SDA low. On BL233B, 8 extra clock pulses will be seen]

## 18.4.2 Failure to send NACK

J0C

[set mode to not send ack after reads. this gets us halfway through a read operation] : **S4000S4101**

[write all 0's to a PCF8574. Now read back 1 byte. BL233 sends ack, so slave expects another read to follow. At this point 8574 is outputting 1<sup>st</sup> data bit (0)]

[STOP fails because 8574 is holding SDA low. On BL233B, 8 extra clock pulses will be seen]

## 18.5 Manually Checking SDA and SCL

Software can check for this condition (and any other bus faults) by using the **Q** command to directly read the port pins and check that the SCL and SDA pins are high after an I2C Stop has been sent. With the BL233A, software could use the **O** command to explicitly toggle SCL 8 times to clear the problem.

## 19 Getting Started

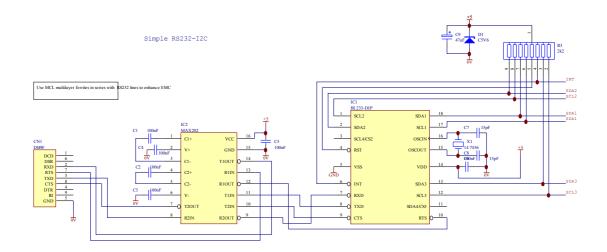

It is best to get a built up I2C-2-PC adaptor for development. This will save you time, and it is fully tested! It is also good to have a very simple I2C chip to try such as a PCF8574.

Baud Rate is *57600 baud*, *N81*, *RTS/CTS* handshaking recommended.

Crystal should be 14.7456 Mhz

Unused pins should be pulled up, and *not* left floating.

Serial data pins must be inverted by a driver chip such as MAX202 before you connect to RS232 cables.

Serial data pins can be directly connected to microprocessor UART pins.

When you power-up or rest the BL233 it sends its string "HI I2C v118"

When you send a "?" it will reply with 2 chars eg "18"

Install Realterm on a windows machine. Realterm has special tabs for sending commands to the BL233. These buttons send the commands to the BL233 as plain ASCII text. You will see all the commands sent on the terminal screen and all the replies from the BL233 in a different color. Remember: there is no special api, and no special magic in Realterm, it is only sending the simple ASCII that you see on the screen.

You can use Realterm to send your commands to the BL233. Once you are able to control your chip and you know what the returned data is like, then you are ready to begin programming your application. It is very easy and quick to get your application going when you know all the commands work, and you have samples of all the returned data.

## 20 Example Applications

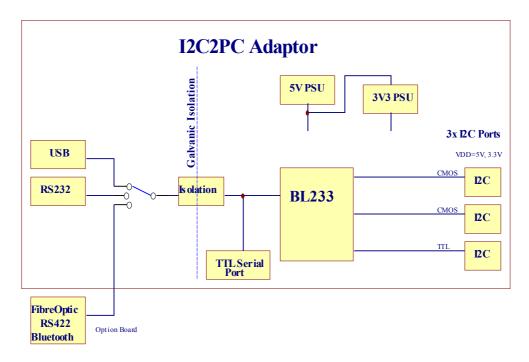

## 20.1 I2C-2-PC: Dual Interface USB & RS232 to I2C Adaptor